Quick announcement, we have a few spots left in our beta tester program for researchers. Requests should be sent to [email protected] along with a short bio and description of your intended application.

Thank you all for the interest you have shown, we have successfully completed our tester program. Stay tuned for updates and a big announcement in late January.

We are quickly nearing a point with software support where we will be confident in doing a general release after doing a little clean up on the code. The soon to be released software support will be completely open source and will contain VHDL and FX3 source code, Linux drivers, user mode utilities, and a simple GNURadio block.

Additionally, we’ve been making great progress on the basic modulation scheme examples. One of the introductory tutorials explains the the development of a wireless UART bridge starting from scratch. Before complicating the examples with too much embedded and driver development, we are utilizing the onboard Cyclone 4 FPGA to modulate data using FSK and demodulate it on the receiving end.

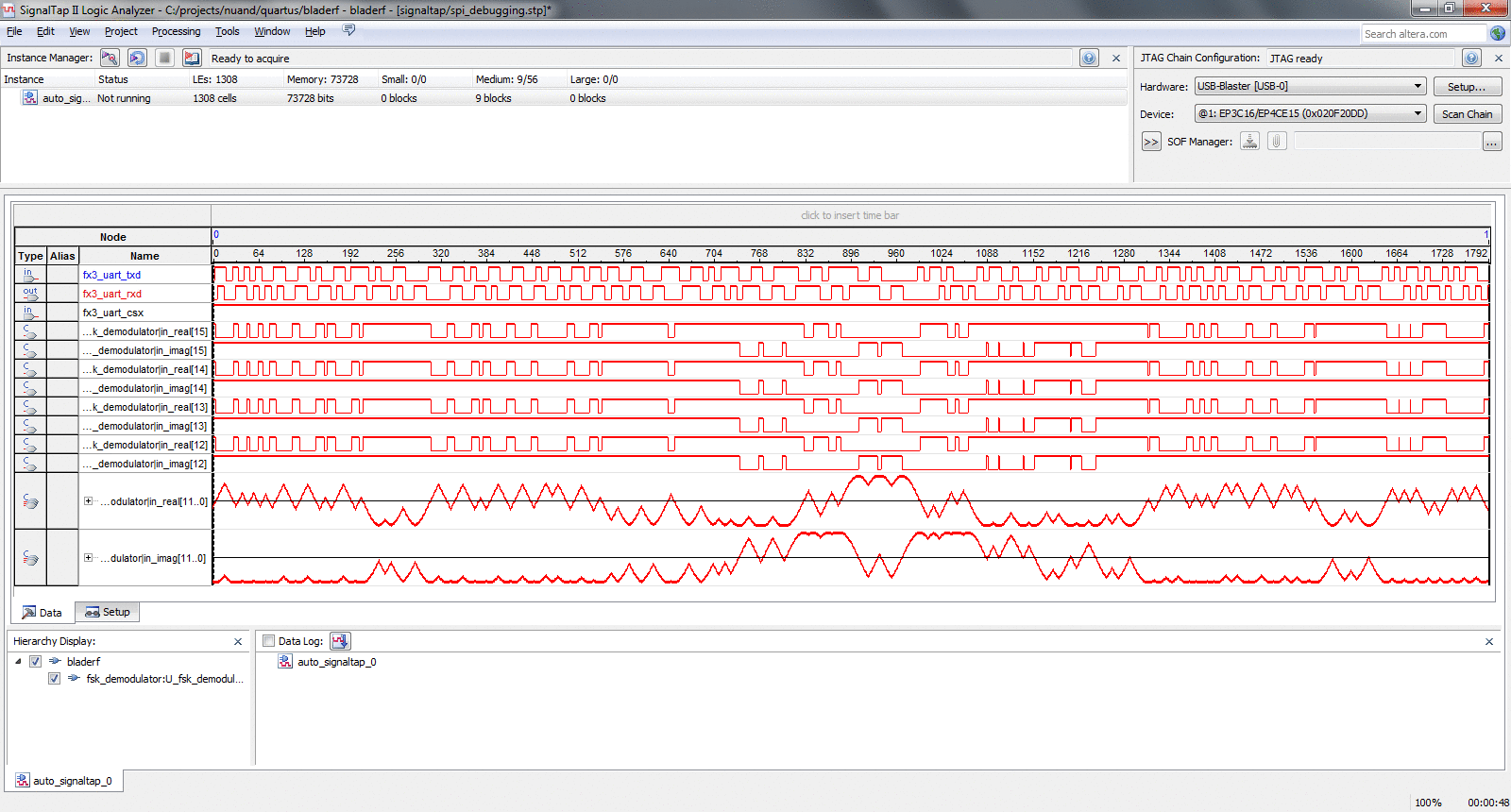

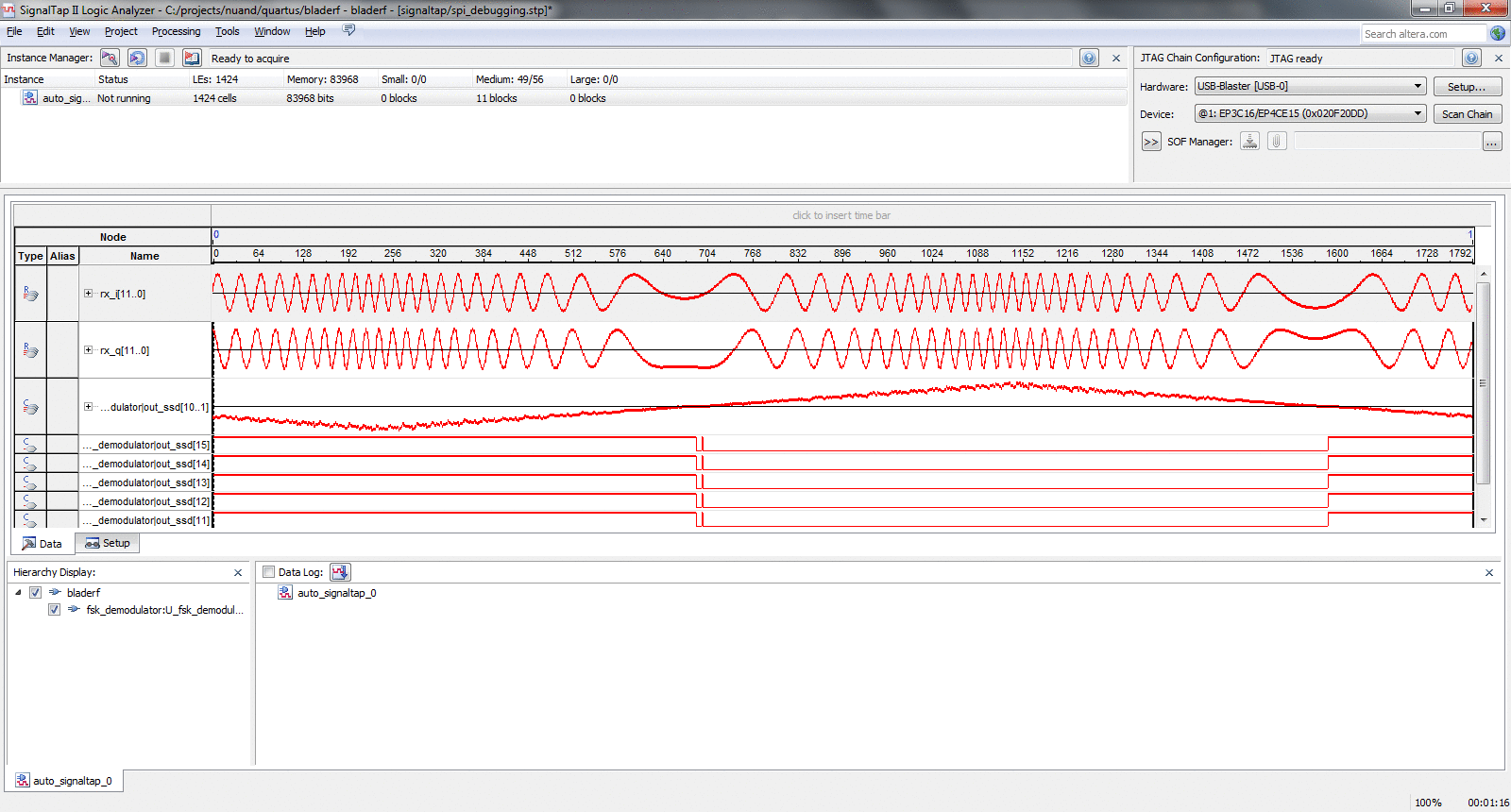

The first screenshot shows signals internal to the FPGA captured using a soft-logic analyzer known as SignalTap. Data that is received by the FPGA on fx3_uart_txd is modulated and turned into I and Q samples that are rendered using the analog visualizer in SignalTap. The FSK modem is in loopback mode in this example, this allows us to measure the group delay by counting the number of clock cycles it takes a bit to come back around, in this case it’s roughly 45 clock cycles at 100MHz, or 450ns. The demodulation signals, specifically I and Q are shown in the bottom SignalTap capture.