Description

Made in USA

Kit contains:

- bladeRF xA9 (301KLE Cyclone V FPGA)

- USB 3.0 SS cable

Optional accessories:

More Information:

- Product Datasheet

- Getting Started guide on bladeRF wiki

- bladeRF-wiphy

- EU Declaration

- bladeRF 2.0 micro Brief

- Schematics REV 1.4

- Schematics REV 1.3

- Mechanical DXF File

- Mechanical Estimate STEP File

- Software Support and Additional Resources

Description:

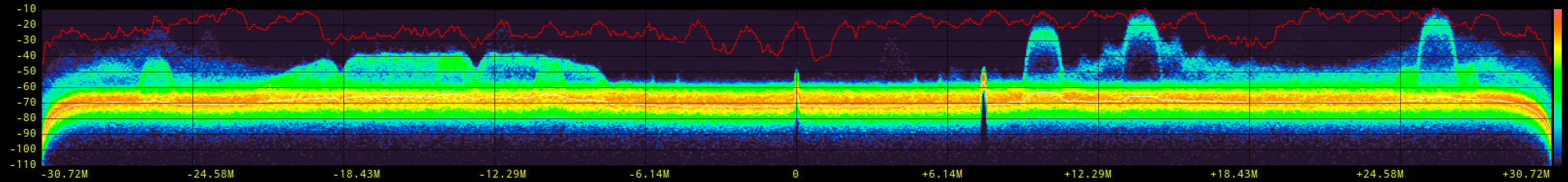

The bladeRF 2.0 micro xA9 is the next generation Software Defined Radio (SDR) offering a frequency range of 47MHz to 6GHz, 61.44MHz sampling rate (capable of up to 122.88MHz), and 2×2 MIMO streaming. Packed into a small form factor, the bladeRF 2.0 micro was designed for high performance as well as mobile applications. Through libbladeRF the bladeRF 2.0 micro is compatible with GNURadio, GQRX, SDR-Radio, SDR#, gr-fosphor, SoapySDR, and more on Windows, Linux and macOS.

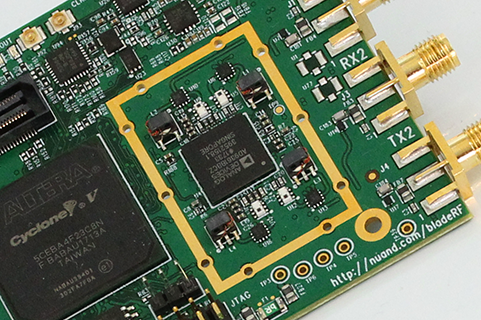

The RF shield cap protects sensitive RF components from Electromagnetic Interference (EMI) and provides additional thermal dissipation, allowing the bladeRF 2.0 micro to operate in challenging environments.

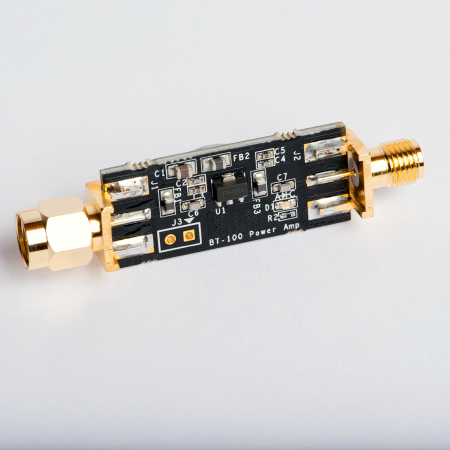

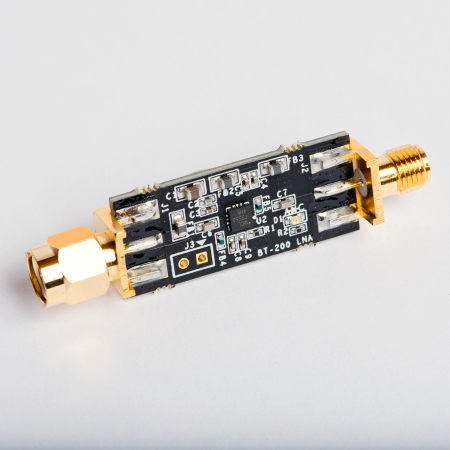

All of the RF SMA ports are capable of providing power over bias-tee circuitry to wideband amplifiers and pre-amps. Power to bias-tee peripherals is fully software controllable, providing maximal operational flexibility. Currently, the official bias-tee peripherals include the BT-100, a wideband power amplifier for TX, and the BT-200, a wideband low noise amplifier for RX.

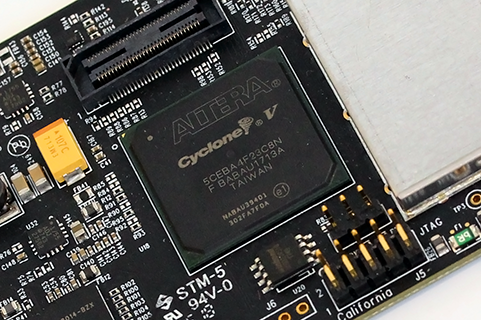

At the core of the bladeRF 2.0 micro is the latest generation Cyclone V FPGA from Intel (formerly Altera). The xA9 features a 301KLE FPGA of which about 292KLE are available and user programmable. The largest-in-class FPGA is ideal for accelerating modems in HDL.

An advanced clocking architecture allows the bladeRF 2.0 micro to receive and provide its 38.4MHz fundamental clock from and to other devices. Additionally, an on-board PLL allows the bladeRF 2.0 micro to tame its VCTCXO to a 10MHz reference signal. The xA9 features a highly accurate and stable oscillator. The on-board DAC sets the frequency trim of the oscillator to a factory calibrated value.

The Power Distribution Network (PDN) of the bladeRF 2.0 micro features an intricate combination of low noise and high efficiency switch mode and linear power regulators. While the bladeRF 2.0 micro can be run solely from USB bus power, an external power source can be supplied to ensure maximal linear performance of bias-tee peripherals. The PDN features an auto selection and hold-over circuitry to optimize power draw between USB bus and external DC power.

The bladeRF 2.0 micro can run in headless without needing to be connected to a PC or SBC. The on-board flash is large enough to hold any size FPGA image for the xA9.

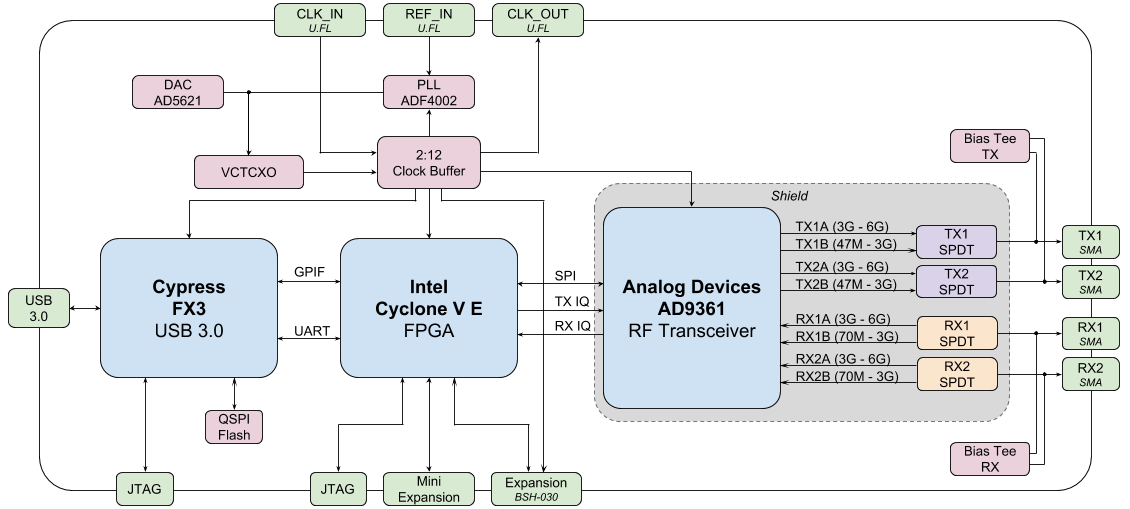

Block Diagram:

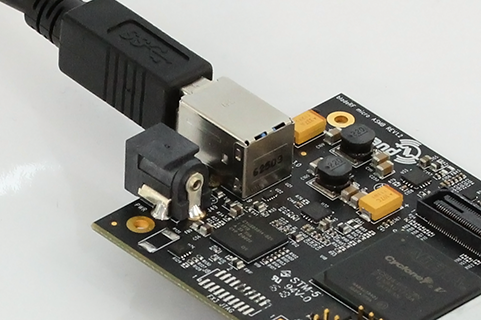

High speed, low latency and increased power delivery over a single cable: USB 3.0 Superspeed is the perfect interface for a wide bandwidth radio front end to modern computers. The Cypress FX3 microcontroller is the ideal solution with a powerful ARM9 processor and enough bandwidth to saturate the full duplex 5Gbps USB 3.0 link.

An Altera Cyclone V FPGA provides the interface between the FX3 and RF transceiver. This FPGA has single-cycle access embedded memory, hard 18×18 multipliers for dedicated DSP and many general logic elements ready to be programmed.

The Analog Devices AD9361 is a fully integrated, high performance RF transceiver. Made for next generation wireless protocols, this transceiver is capable of handling anything from simple FM audio to the latest 5G LTE standard to whatever the future may hold.

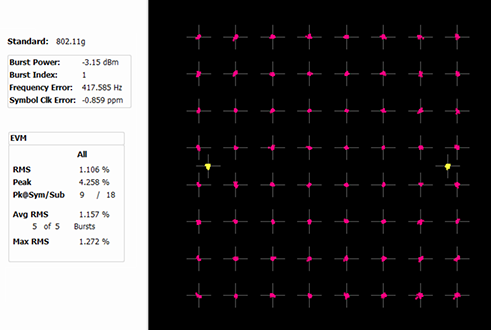

The bladeRF’s design has been tested and verify to meet our very high standards. Every device is capable of effortlessly and faithfully transceiving even the highest order modulations. At peak RF performance, the bladeRF can occupy 2×2 56MHz of bandwidth over its operating frequency range without significant distortions and EVMs around 1%.