Hello, Colleagues

In the document "Adding custom VHDL modules or Altera IP" (https://github.com/Nuand/bladeRF/wiki/F ... -altera-ip) the procedure of adding VHDL-modules, which are developed by customer, is described . Could I add custom Verilog -modules, not the .vhd-modules? Will the addition procedure change?

Thanks, Dmitry_K

Adding custom Verilog modules

-

bglod

- Posts: 201

- Joined: Thu Jun 18, 2015 6:10 pm

Re: Adding custom Verilog modules

Absolutely! The procedure is similar, just change the -name parameter of the set_global_assignment command from "-name VHDL_FILE" to "-name VERILOG_FILE". Remember that as a limitation of Quartus (and Xilinx Vivado), direct instantiation of a verilog module inside a VHDL design is not supported. Instead, you'll have to do the "old-fashioned" VHDL component declaration prior to instantiating the component, unfortunately.

Electrical Engineer

Nuand, LLC.

Nuand, LLC.

-

Dmitry_K

- Posts: 7

- Joined: Mon Oct 23, 2017 9:03 am

Re: Adding custom Verilog modules

Thank You, bglod.bglod wrote: ↑Tue Jan 23, 2018 10:20 am Absolutely! The procedure is similar, just change the -name parameter of the set_global_assignment command from "-name VHDL_FILE" to "-name VERILOG_FILE". Remember that as a limitation of Quartus (and Xilinx Vivado), direct instantiation of a verilog module inside a VHDL design is not supported. Instead, you'll have to do the "old-fashioned" VHDL component declaration prior to instantiating the component, unfortunately.

-

Dmitry_K

- Posts: 7

- Joined: Mon Oct 23, 2017 9:03 am

Re: Adding custom Verilog modules

In order to understanding the algorithm of custom Verilog modules adding, I develop Verilog-module, which is used for the same function as an example, described in "Tutorial: Blinking some LEDs". To instantiate my Verilog-module in bladerf-hosted.vhd I followed the steps below:

Step_1. I have run the build script to build the FPGA bitstream for non-modernized project and got success.

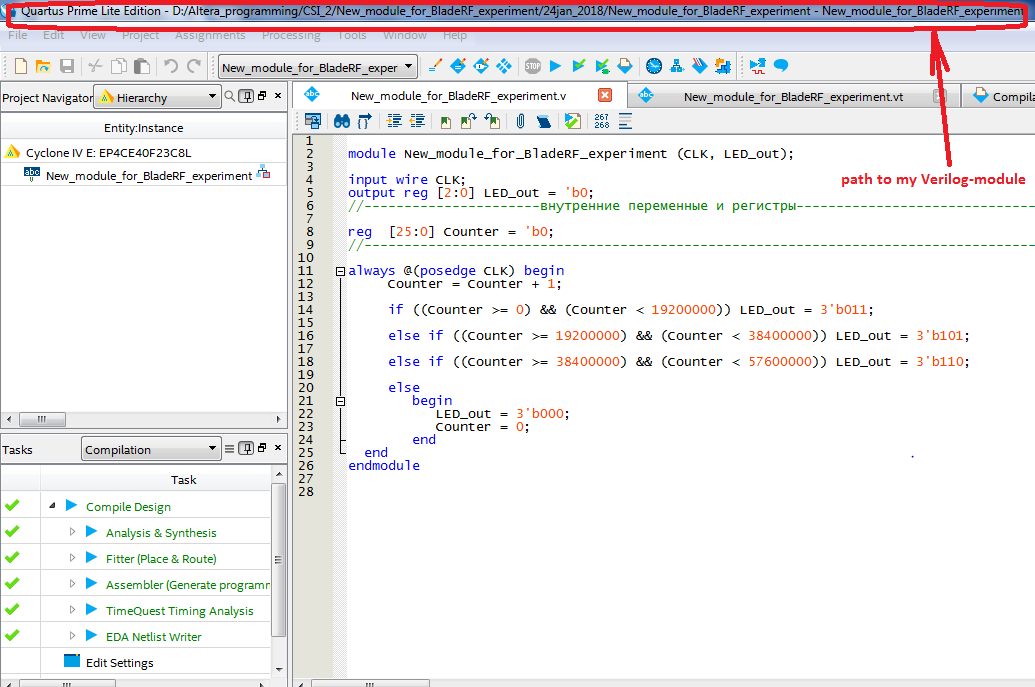

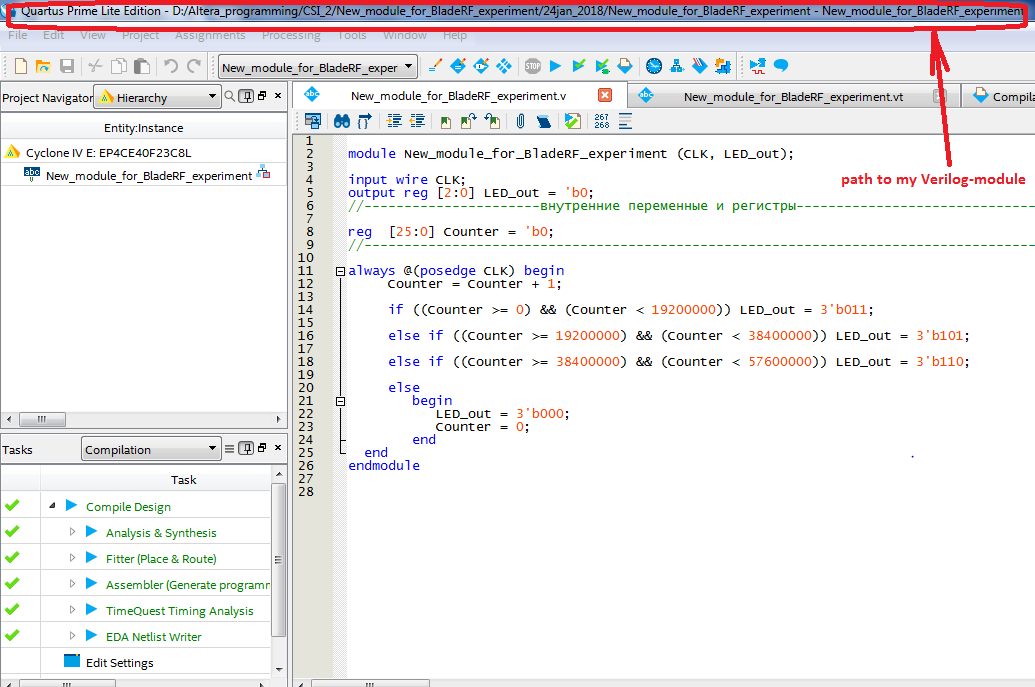

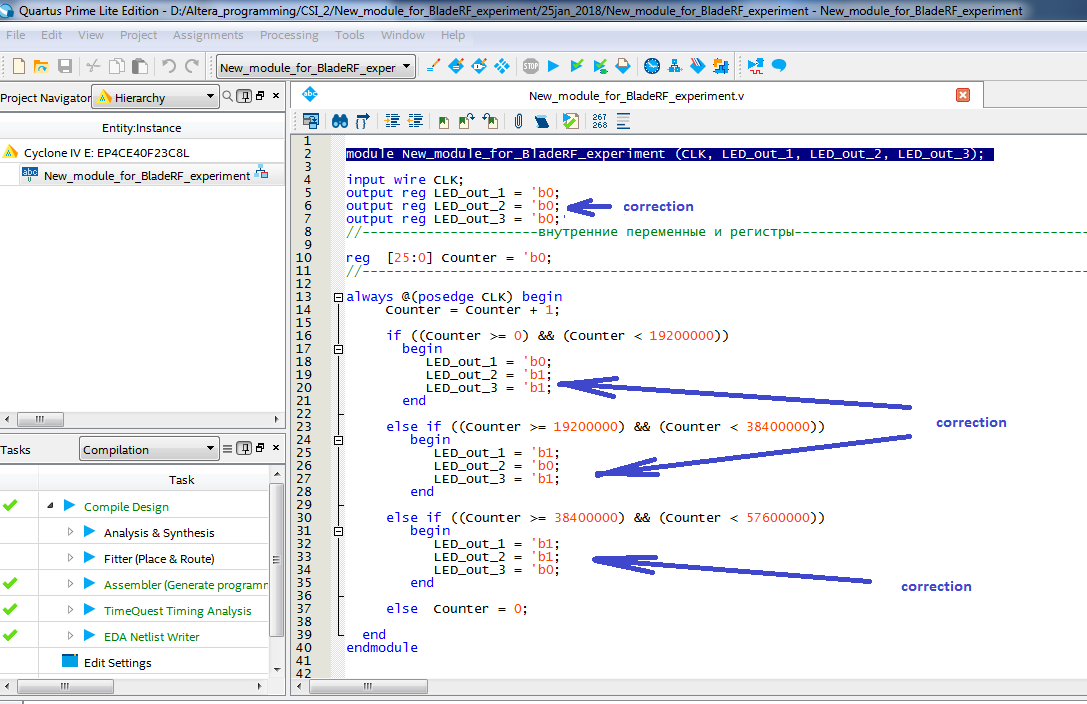

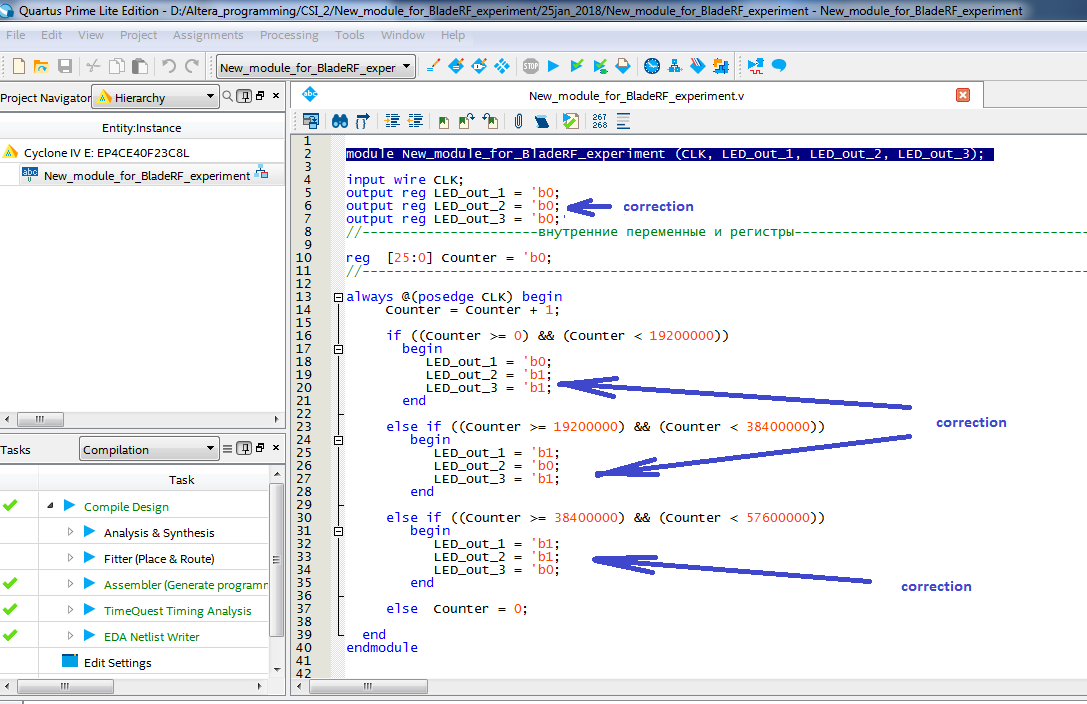

Step_2. I wrote a Verilog file for my custom module. I repeat: that module performs the same function as an example, described in "Tutorial: Blinking some LEDs":

Img 1. New_module_for_BladeRF_experiment.

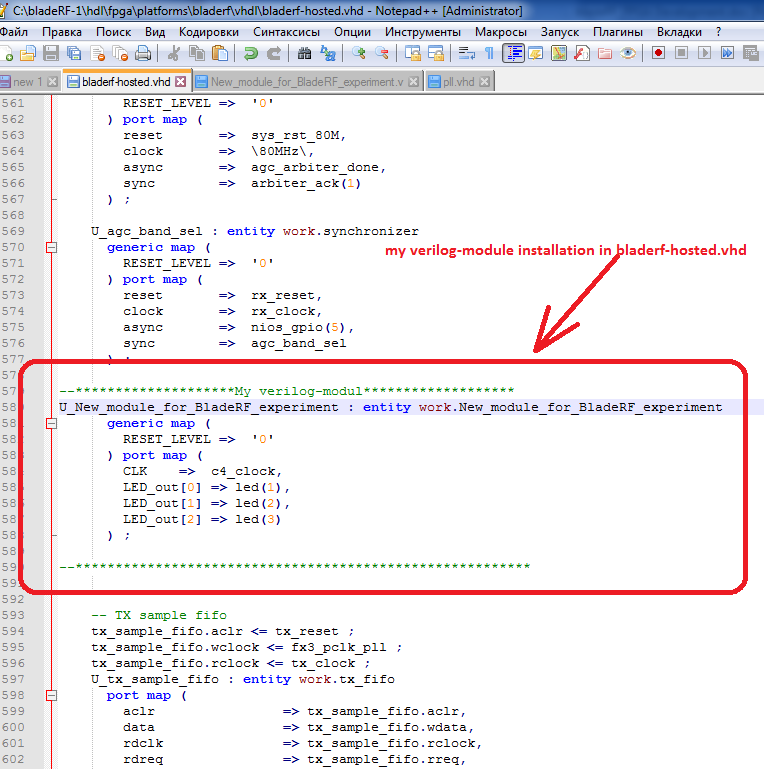

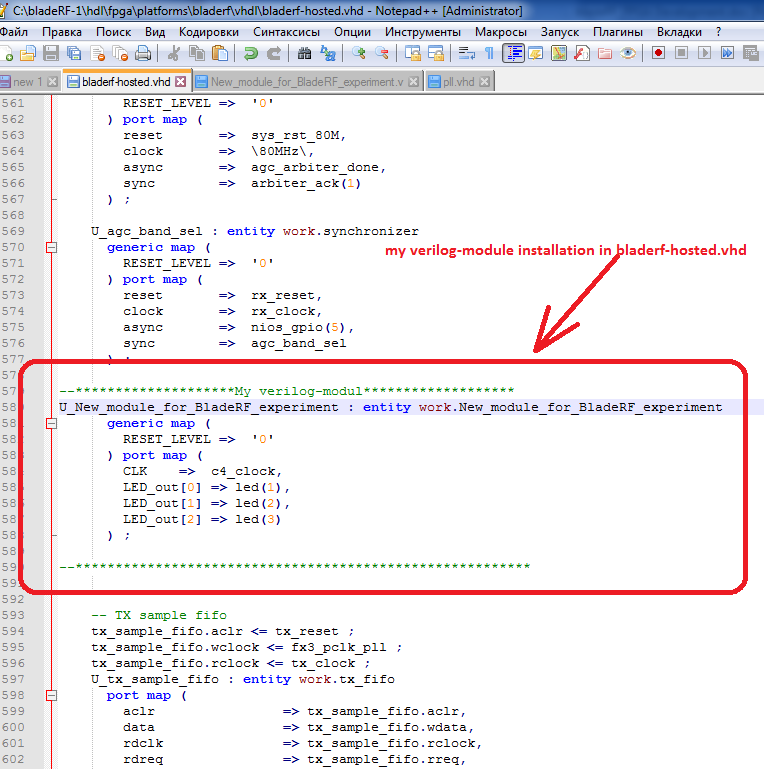

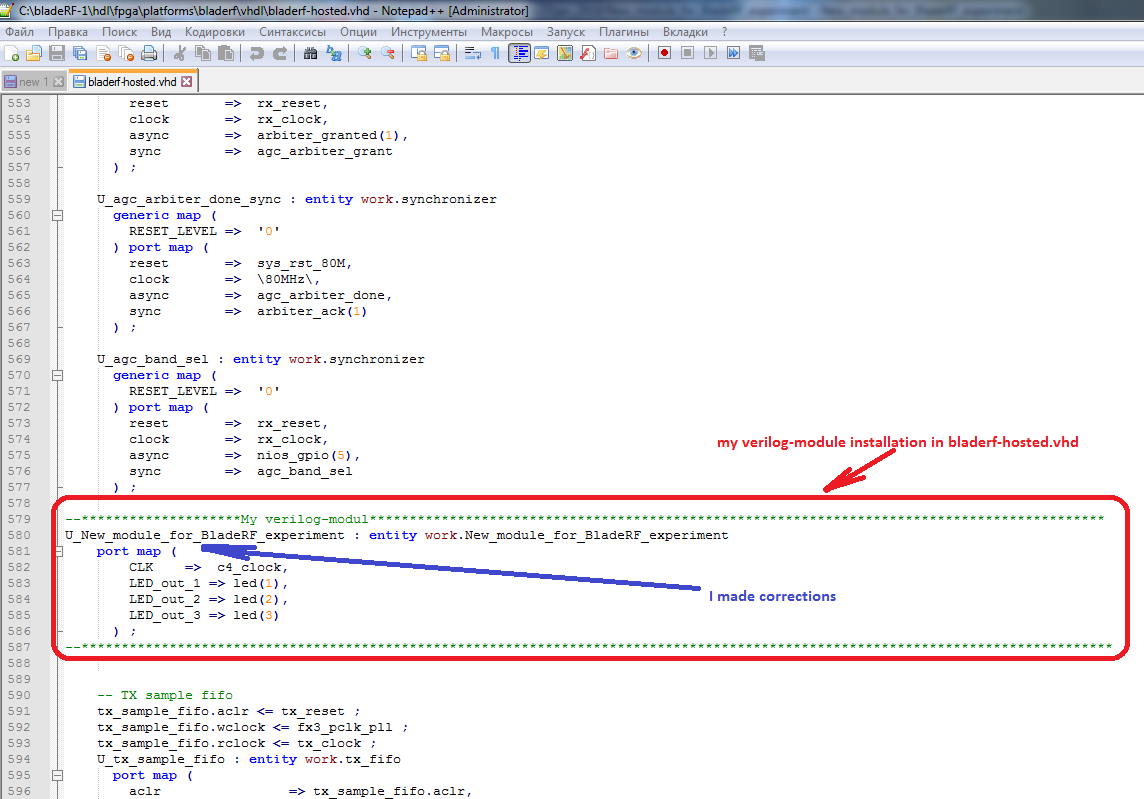

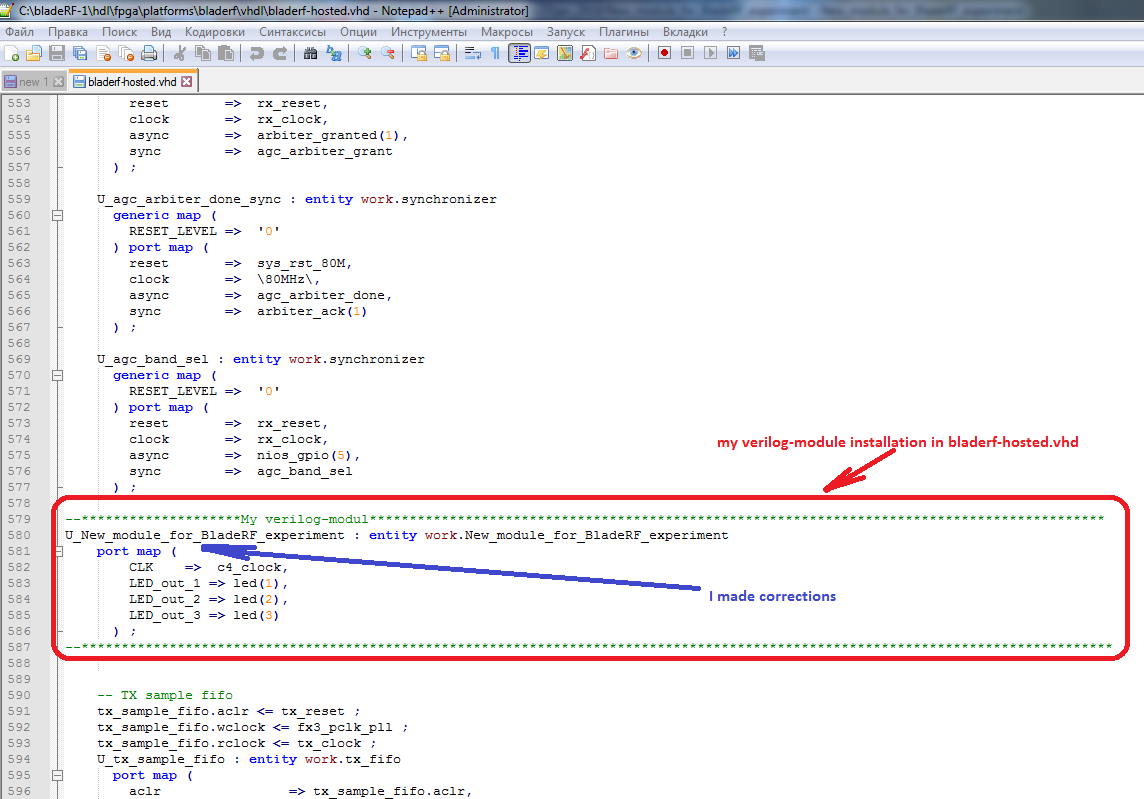

Step_3. I instantiated the module in bladerf-hosted.vhd:

--********************My verilog-modul************************************

U_New_module_for_BladeRF_experiment : entity work.New_module_for_BladeRF_experiment

generic map (

RESET_LEVEL => '0'

) port map (

CLK => c4_clock,

LED_out[0] => led(1),

LED_out[1] => led(2),

LED_out[2] => led(3)

) ;

--************************************************************************

Img 2. New_module installation in bladerf-hosted.vhd

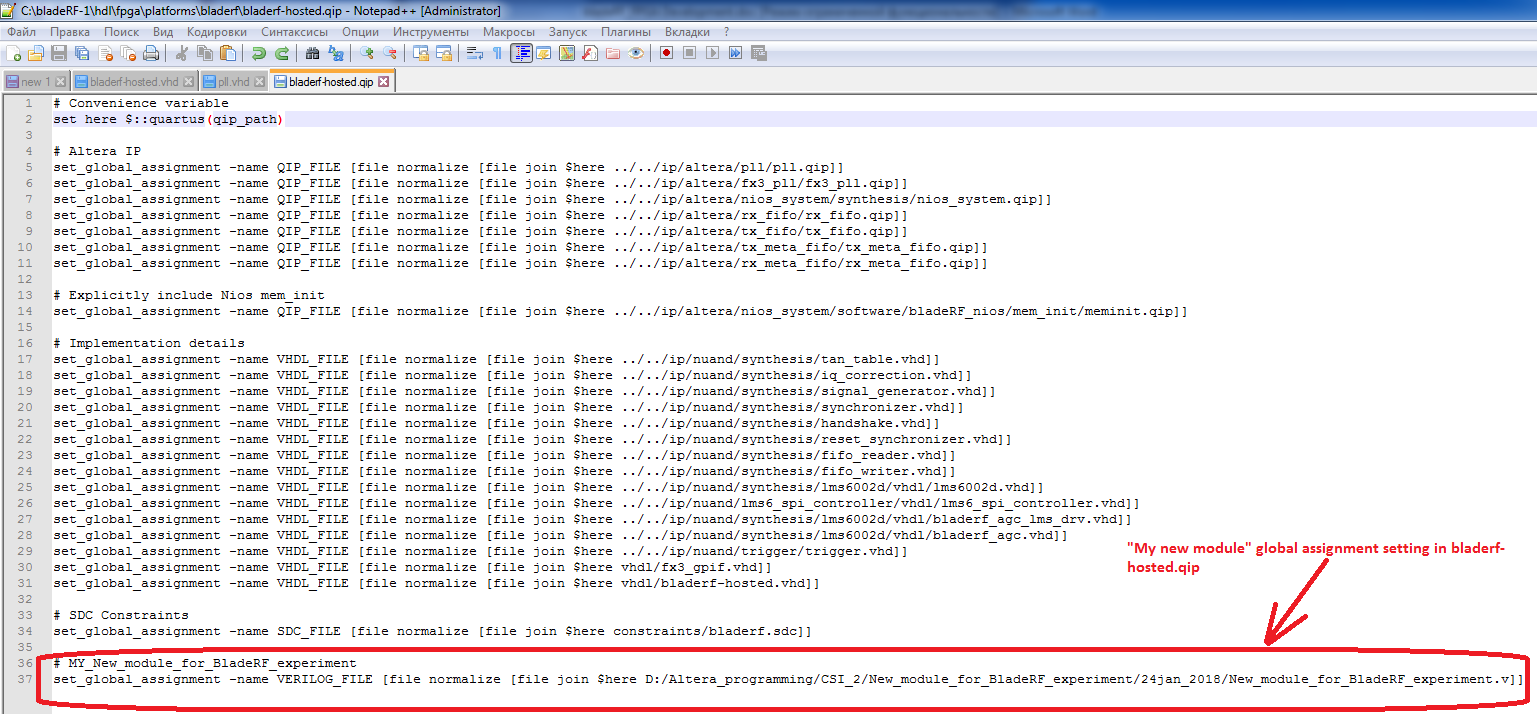

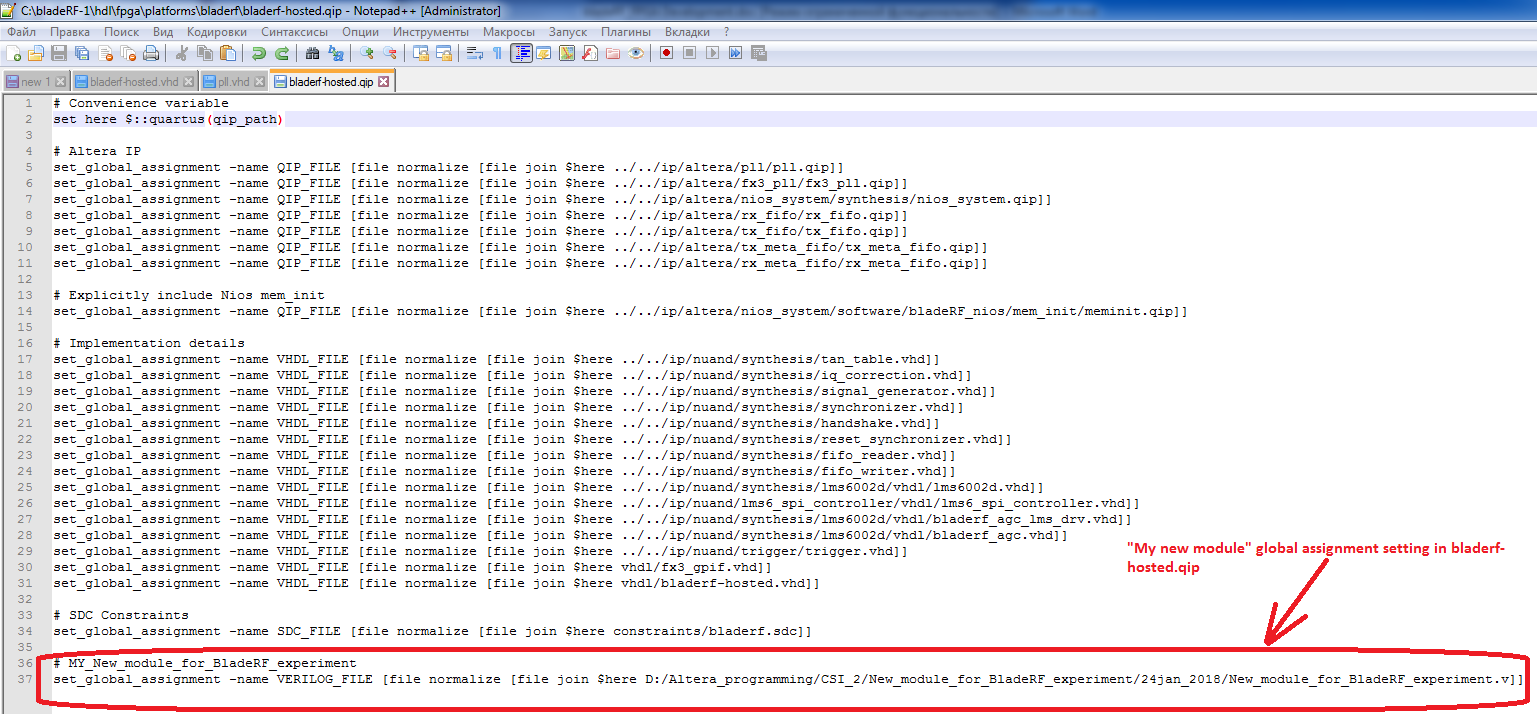

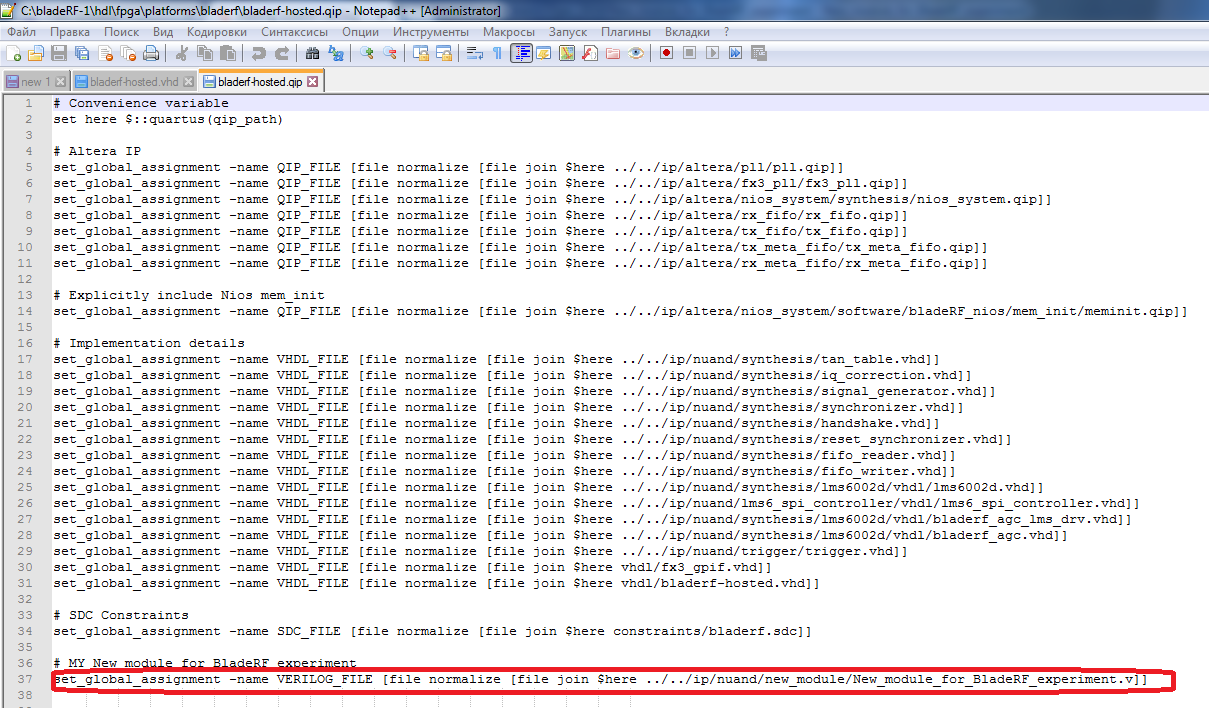

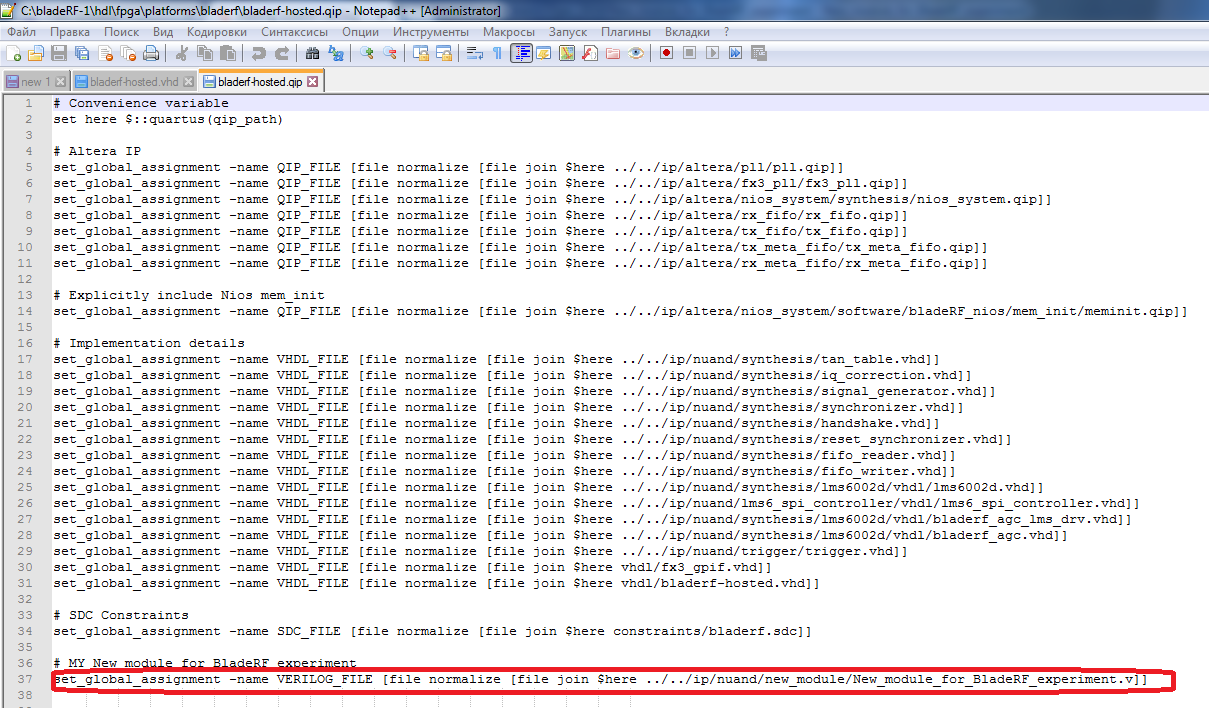

Step_4. I opened bladerf-hosted.qip and add the relative path to my module:

set_global_assignment -name VERILOG_FILE [file normalize [file join $here D:/Altera_programming/CSI_2/New_module_for_BladeRF_experiment/24jan_2018/New_module_for_BladeRF_experiment.v]]

Img.3. New_module_adding_in_bladerf_hosted_qip

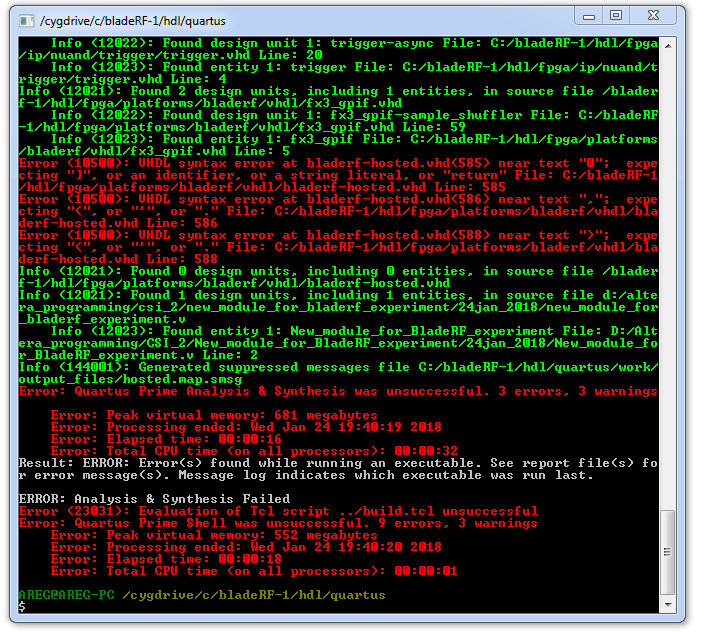

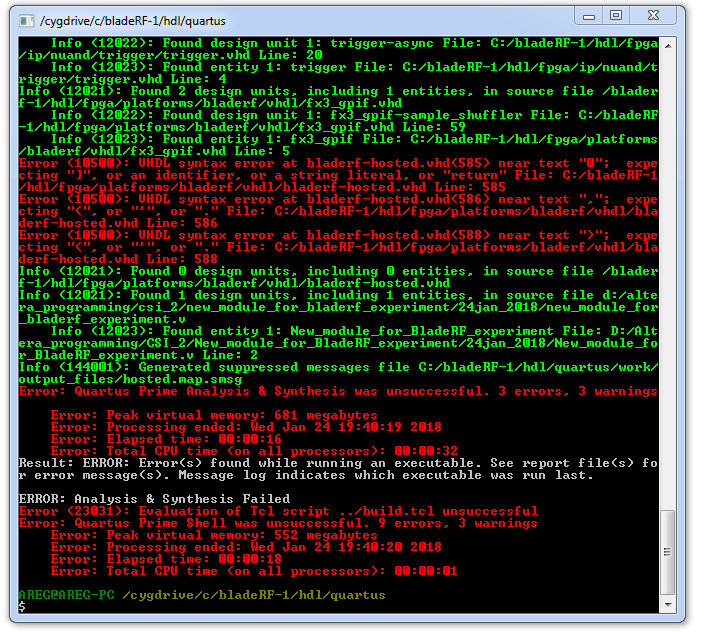

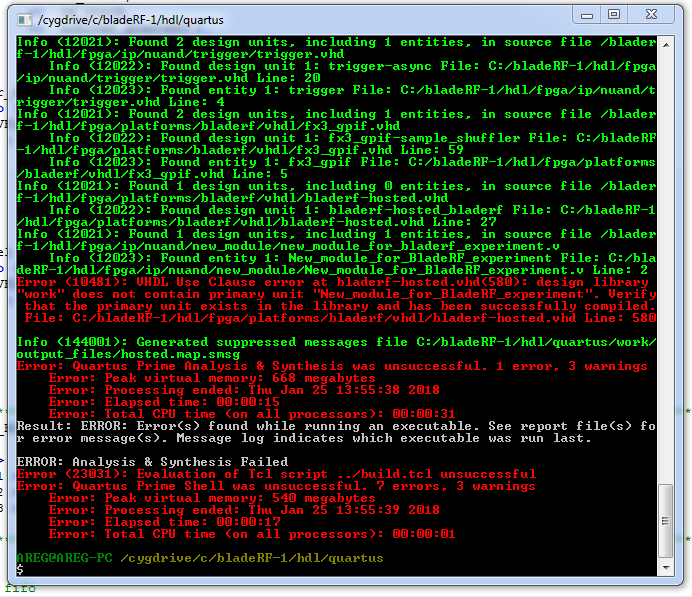

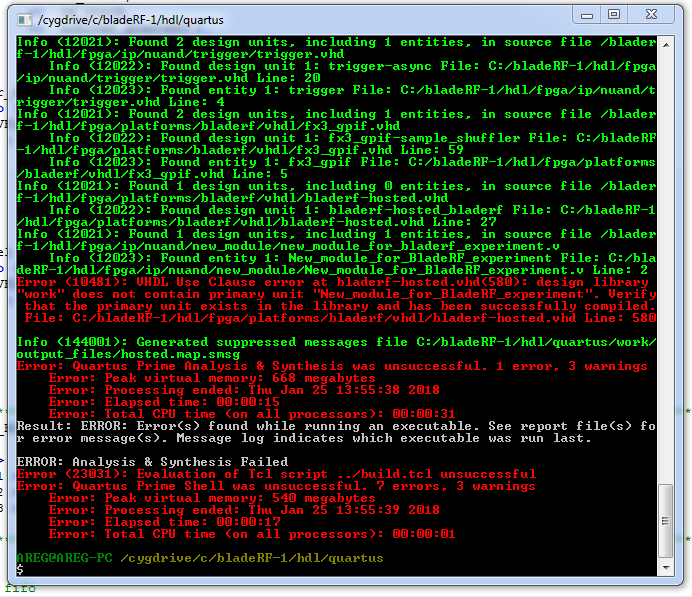

Step_5. I have run the build script to build the FPGA bitstream for modernized project and got unsuccess:

Img 4. New_module_Project_building_ERROR

WHAT IS THE MISTAKE?

Step_1. I have run the build script to build the FPGA bitstream for non-modernized project and got success.

Step_2. I wrote a Verilog file for my custom module. I repeat: that module performs the same function as an example, described in "Tutorial: Blinking some LEDs":

Img 1. New_module_for_BladeRF_experiment.

Step_3. I instantiated the module in bladerf-hosted.vhd:

--********************My verilog-modul************************************

U_New_module_for_BladeRF_experiment : entity work.New_module_for_BladeRF_experiment

generic map (

RESET_LEVEL => '0'

) port map (

CLK => c4_clock,

LED_out[0] => led(1),

LED_out[1] => led(2),

LED_out[2] => led(3)

) ;

--************************************************************************

Img 2. New_module installation in bladerf-hosted.vhd

Step_4. I opened bladerf-hosted.qip and add the relative path to my module:

set_global_assignment -name VERILOG_FILE [file normalize [file join $here D:/Altera_programming/CSI_2/New_module_for_BladeRF_experiment/24jan_2018/New_module_for_BladeRF_experiment.v]]

Img.3. New_module_adding_in_bladerf_hosted_qip

Step_5. I have run the build script to build the FPGA bitstream for modernized project and got unsuccess:

Img 4. New_module_Project_building_ERROR

WHAT IS THE MISTAKE?

-

bglod

- Posts: 201

- Joined: Thu Jun 18, 2015 6:10 pm

Re: Adding custom Verilog modules

Take a look at lines 585, 586, and 587 in your bladerf-hosted.vhd file as the error is suggesting. The syntax "[0]" is incorrect with the square brackets. In VHDL, to slice an array type, parentheses are used: "(0)". Alternatively, you may simplify your LED_out port map to just "LED_out => led" if you want. The bit indices will remap 2:0 to 3:1 automatically. What you did is fine too as it's more explicit for the reader and shows that the index remapping is intentional.

Later, you will get another error stating that your module was not found in library work. This is because you cannot directly instantiate Verilog modules (limitation of Quartus, and last I checked Vivado had the same limitation). Instead, you'll have to declare the component first, then instantiate the component.

You will get yet another error about the RESET_LEVEL parameter in your generic map. This parameter doesn't exist in your Verilog design. I assume it's in your generic map because you copy/pasted the previous entity instantiation. Either declare it in your Verilog, or delete the generic map section altogether. The latter seems more appropriate in this example.

Later, you will get another error stating that your module was not found in library work. This is because you cannot directly instantiate Verilog modules (limitation of Quartus, and last I checked Vivado had the same limitation). Instead, you'll have to declare the component first, then instantiate the component.

You will get yet another error about the RESET_LEVEL parameter in your generic map. This parameter doesn't exist in your Verilog design. I assume it's in your generic map because you copy/pasted the previous entity instantiation. Either declare it in your Verilog, or delete the generic map section altogether. The latter seems more appropriate in this example.

Electrical Engineer

Nuand, LLC.

Nuand, LLC.

-

Dmitry_K

- Posts: 7

- Joined: Mon Oct 23, 2017 9:03 am

Re: Adding custom Verilog modules

Dear, bglod

Today I made some correection according to Your replay.

Step_1 I was change the Verilog-source of my module in order to simplify my LED_out port map:

Step_2 I changed the declaration way of my module instance in bladerf-hosted.vhd - in according to Your advice, I deleted the generic map section altogether:

--********************My verilog-modul********************************************************************************************

U_New_module_for_BladeRF_experiment : entity work.New_module_for_BladeRF_experiment

port map (

CLK => c4_clock,

LED_out_1 => led(1),

LED_out_2 => led(2),

LED_out_3 => led(3)

) ;

--*********************************************************************************************************************************

Step_3 I place Verilog-source file of my module in the active project folder \bladeRF-1\hdl\fpga\ip\nuand\new_module\New_module_for_BladeRF_experiment.v and changed bladerf-hosted.qip file (I changed relative path to my module):

Step_5 I have run the build script to build the FPGA bitstream for modernized project and got unsuccess again. But errors quantity was less (only 1 error):

How to fix this error?

Thanks.

Today I made some correection according to Your replay.

Step_1 I was change the Verilog-source of my module in order to simplify my LED_out port map:

Step_2 I changed the declaration way of my module instance in bladerf-hosted.vhd - in according to Your advice, I deleted the generic map section altogether:

--********************My verilog-modul********************************************************************************************

U_New_module_for_BladeRF_experiment : entity work.New_module_for_BladeRF_experiment

port map (

CLK => c4_clock,

LED_out_1 => led(1),

LED_out_2 => led(2),

LED_out_3 => led(3)

) ;

--*********************************************************************************************************************************

Step_3 I place Verilog-source file of my module in the active project folder \bladeRF-1\hdl\fpga\ip\nuand\new_module\New_module_for_BladeRF_experiment.v and changed bladerf-hosted.qip file (I changed relative path to my module):

Step_5 I have run the build script to build the FPGA bitstream for modernized project and got unsuccess again. But errors quantity was less (only 1 error):

How to fix this error?

Thanks.

-

bglod

- Posts: 201

- Joined: Thu Jun 18, 2015 6:10 pm

Re: Adding custom Verilog modules

You didn't have to make a separate output port for each LED. You could have kept it as a single bus of width 3 and just have the single port map. It would look something like this:

Or, you could have done the following for explicit indexing:

For the error you have now, please read my previous response. You cannot directly instantiate a verilog module in VHDL. You need to declare the component first. Take a look here:

https://www.doulos.com/knowhow/vhdl_des ... port_maps/

https://www.altera.com/support/support- ... 1_444.html

Code: Select all

port map (

module_bus => toplevel_bus -- the left side is a 2:0 bus, the right is 3:1

);

Code: Select all

port map (

module_bus(2) => toplevel_bus(3),

module_bus(1) => toplevel_bus(2),

module_bus(0) => toplevel_bus(1)

);

https://www.doulos.com/knowhow/vhdl_des ... port_maps/

https://www.altera.com/support/support- ... 1_444.html

Electrical Engineer

Nuand, LLC.

Nuand, LLC.